### **User's Guide**

## Agilent Technologies N5102A Baseband Studio Digital Signal Interface Module

Due to our continuing efforts to improve our products through firmware and hardware revisions, N5102A module design and operation may vary from descriptions in this guide. We recommend that you use the latest revision of this guide to ensure you have up-to-date product information. Compare the print date of this guide (see bottom of page) with the latest revision, which can be downloaded from the following website:

www.agilent.com/find/basebandstudio

Manufacturing Part Number: N5102-90001

Printed in USA

August 2003

© Copyright 2003 Agilent Technologies, Inc.

#### **Notice**

The material contained in this document is provided "as is", and is subject to being changed, without notice, in future editions.

Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied with regard to this manual and to any of the Agilent products to which it pertains, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or any of the Agilent products to which it pertains. Should Agilent have a written contract with the User and should any of the contract terms conflict with these terms, the contract terms shall control.

#### **Questions or Comments about our Documentation?**

We welcome any questions or comments you may have about our documentation. Please send us an E-mail at **sources\_manuals@am.exch.agilent.com**.

| 1. Insta |                                                   |      |

|----------|---------------------------------------------------|------|

|          | Safety Information                                | 2    |

|          | Warnings, Cautions, and Notes                     | 2    |

|          | Instrument Markings                               | 2    |

|          | General Safety Considerations                     | 3    |

| (        | Getting Started                                   | 4    |

|          | Checking the Shipment                             | 4    |

|          | Meeting Electrical and Environmental Requirements | 4    |

|          | Ventilation                                       | 5    |

|          | Line Settings                                     | 5    |

|          | Connecting the AC Power Cord                      | 6    |

|          | AC Power Cord Localization                        | 6    |

|          | Proper Usage and Cleaning.                        | 6    |

| (        | Connecting the N5102A Module to the ESG/PSG.      | 8    |

| •        | Operation Verification.                           | . 11 |

| ]        | Regulatory Information                            | . 13 |

|          | Statement of Compliance                           | . 13 |

|          | Assistance                                        | . 13 |

|          | Certification                                     | . 13 |

|          | Declaration of Conformity                         | . 13 |

|          | Compliance with German Noise Requirements         | . 13 |

|          | Compliance with Canadian EMC Requirements         | . 14 |

| 2. Over  | view                                              |      |

| ]        | Features                                          | .16  |

|          | Front Panel                                       |      |

|          | 1. DC Power Receptacle                            |      |

|          | 2. Power LED                                      |      |

|          | 3. Status LED                                     |      |

|          | 4. Digital Bus Connector.                         |      |

|          | 5. Freq Ref Connector                             |      |

| ]        | Rear Panel                                        |      |

|          | 1. Ext Clock In Connector.                        |      |

|          | 2. Clock Out Connector.                           |      |

|          | 3. Device Interface Connector.                    | .21  |

| 3. DUT   | Connections                                       |      |

|          | Break-Out Boards                                  | 2/   |

| 1        | Dioux Out Dourds                                  | . 2- |

|                   | Dual 20-Pin Break-Out Board                    | 25 |

|-------------------|------------------------------------------------|----|

|                   | Dual 38-Pin Break-Out Board                    | 27 |

|                   | Dual 40 Pin Break-Out Board                    | 29 |

|                   | Single 68-Pin SCSI Style Break-Out Board       | 31 |

|                   | Dual 100-Pin Break-Out Board                   | 32 |

|                   | Device Interface Connector                     | 34 |

|                   | Input and Output Clock Signals                 | 36 |

|                   | Data Lines                                     | 37 |

|                   | DC Supply                                      | 38 |

|                   | VCCIO                                          | 38 |

|                   | Device Interface Mating Connector              | 39 |

| 4. O <sub>I</sub> | <b>Operation</b>                               |    |

|                   | Clock Timing                                   | 44 |

|                   | Clock and Sample Rates                         | 44 |

|                   | Clock Source.                                  | 47 |

|                   | Common Frequency Reference                     | 48 |

|                   | Clock Timing for Parallel Data.                | 52 |

|                   | Clock Timing for Parallel Interleaved Data     | 54 |

|                   | Clock Timing for Serial Data                   | 56 |

|                   | Clock Timing for Phase and Skew Adjustments    | 56 |

|                   | Connecting the Clock Source and DUT.           | 58 |

|                   | Operating the N5102A Module                    |    |

|                   | Setting up the Signal Generator Baseband Data  | 60 |

|                   | Accessing the N5102A Module User Interface     | 60 |

|                   | Choosing the Logic Type and Port Configuration | 61 |

|                   | Selecting the Data Parameters                  | 62 |

|                   | Configuring the Clock Signal                   | 64 |

|                   | Generating Digital Data                        | 68 |

|                   | Setup Checklist                                | 69 |

| 5. Sc             | Softkeys and SCPI Commands                     |    |

|                   | Softkey and SCPI Command Descriptions          | 72 |

|                   | 0 deg                                          | 72 |

|                   | 1                                              | 72 |

|                   | 1.5V CMOS                                      | 73 |

|                   | 1.8V CMOS                                      | 73 |

|                   | 2                                              | 73 |

| 2's Complement         | .74 |

|------------------------|-----|

| 2.5V CMOS              | .74 |

| 3.3V CMOS              | .74 |

| 4                      | .74 |

| 90 deg                 | .75 |

| 180 deg                | .75 |

| 270 deg                | .76 |

| Bit Order MSB LSB      | .76 |

| Clock Phase            | .77 |

| Clock Polarity Neg Pos | .77 |

| Clock Rate             | .77 |

| Clock Setup            | .78 |

| Clock Skew             | .79 |

| Clock Source           | .79 |

| Clocks Per Sample      | .79 |

| Data Setup             | .80 |

| Data Type              | .80 |

| Device                 | .81 |

| Device Intfc           | .81 |

| Diagnostics            | .81 |

| Dig Bus Cable          | .81 |

| External               | .82 |

| Frame Polarity Neg Pos | .82 |

| Gain, Offset & Scaling | .82 |

| I Gain                 | .83 |

| I Offset               | .83 |

| Internal               | .83 |

| IQ Polarity Neg Pos    | .83 |

| Logic Type             | .84 |

| Loop Back Test Type    | .84 |

| LVDS                   | .84 |

| LVTTL                  | .85 |

| N5102A Dig Bus         | .85 |

| N5102A Interface       | .85 |

| N5102A Off On          | .85 |

| Negate I Data Off On   | .86 |

| Negate Q Data Off On   | .86 |

| Numeric Format         | .87 |

|      | Offset Binary                                   | 87  |

|------|-------------------------------------------------|-----|

|      | Par IQ Intrlvd                                  | 87  |

|      | Par QI Intrlvd                                  | 87  |

|      | Parallel                                        | 87  |

|      | Pre-FIR Samples                                 | 88  |

|      | Port Config                                     | 88  |

|      | Q Gain                                          | 88  |

|      | Q Offset.                                       | 88  |

|      | Reference Frequency                             | 89  |

|      | Rotation                                        | 89  |

|      | Run Loop Back Test                              | 89  |

|      | Samples                                         | 90  |

|      | Scaling                                         | 90  |

|      | Serial                                          | 90  |

|      | SigGen Dig Bus                                  | 90  |

|      | Signal Type IQ IF                               | 91  |

|      | Word Size                                       | 91  |

| 6. T | Troubleshooting                                 |     |

|      | If You Encounter a Problem                      | 94  |

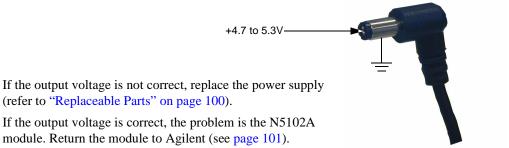

|      | Checking Power Problems                         | 95  |

|      | Running Diagnostic Tests                        | 96  |

|      | Replaceable Parts                               | 100 |

|      | Returning an Instrument to Agilent Technologies | 101 |

# 1 Installation

This chapter provides the following:

- "Safety Information" on page 2

- "Getting Started" on page 4

- "Connecting the N5102A Module to the ESG/PSG" on page  $8\,$

- "Operation Verification" on page 11

- "Regulatory Information" on page 13

#### **Safety Information**

#### Warnings, Cautions, and Notes

The following safety notations are used throughout this manual. Familiarize yourself with each notation and its meaning before operating this product.

# WARNING Warning denotes a hazard. It calls attention to a condition or situation that could result in personal injury or loss of life. Do not proceed beyond a warning until the indicated conditions or situations are fully understood. Caution calls attention to a possible condition or situation that could result in a loss of a user's work, damage, or destruction of the product. Do not proceed beyond a caution until the indicated conditions are fully understood. NOTE Note calls the user's attention to an important point of special information within the text. It provides operational information or additional instructions of which the user should be aware.

#### **Instrument Markings**

The following markings are is used on the N5102A Baseband Studio digital signal interface module. Familiarize yourself with it and its meaning before operating the module.

The CE mark is a registered trademark of the European Community. If this symbol is accompanied by a year, it is the year when the design was proven.

The CSA mark is a registered trademark of the Canadian Standards Association.

The C-Tick Mark is a trademark registered to the Australian Spectrum Management Agency. This indicates compliance with all Australian EMC regulatory information.

This symbol indicates that the center conductor (of the power supply) is positive, and the outer conductor is negative.

This symbol indicates that the input power required is DC.

This symbol indicates compliance with the Canadian Interference-Causing Equipment Standard (ICES-001).

#### **General Safety Considerations**

#### **WARNING**

Personal injury may result if the module cover is removed. There are no operator serviceable parts inside. To avoid electrical shock, refer servicing to qualified personnel.

Chapter 1 3

#### **Getting Started**

#### **Checking the Shipment**

1. Inspect the shipping container for damage.

Signs of damage may include a dented or torn shipping container or cushioning material that indicates signs of unusual stress or compacting.

2. Carefully remove the contents from the shipping container and verify that your order is complete.

The following items are shipped standard with each N5102A Baseband Studio digital signal interface module:

- · user's guide

- documentation CD-ROM

- three-prong AC power cord (specific to geographic location)

- power supply

- proprietary three-meter digital bus cable

- five break-out boards (PC boards with connectors)

- loop back fixture (for troubleshooting)

- Device Interface port mating connector See "Rear Panel" on page 20 for connector locations.

#### **Instrument Dimensions**

Length: 189.9 mm (7.48 in)

Width: 144.8 mm (5.70 in)

Height: 41.6 mm (1.64 in)

#### Meeting Electrical and Environmental Requirements

The N5102A module is designed for use in the following environmental conditions:

- indoor use

- altitudes < 15,000 feet (4,572 meters)

- 0 to 55°C temperatures, unless otherwise specified

• 80% relative humidity (maximum for temperatures up to 31°C, decreasing linearly to 50% relative humidity at 40°C.

CAUTION

This product is designed for use in INSTALLATION CATEGORY II and POLLUTION DEGREE 2, per IEC 61010-1 and 664, respectively.

#### Ventilation

Ventilation holes are located on the front and rear panels of the N5102A module. Do not allow these holes to be obstructed, as they allow air flow through the module.

When installing the module in a cabinet, the convection into and out of the module must not be restricted. The ambient temperature outside the cabinet must be less than the maximum operating temperature of the module by 4°C for every 100 watts dissipated within the cabinet.

#### **CAUTION**

Damage to the module may result when the total power dissipated in the cabinet is greater than 800 watts. When this condition exists, forced convection must be applied.

#### **Line Settings**

The N5102A module requires a power supply that meets the following conditions:

Voltage:

5V

Frequency:

DC

Current:

4.0A

The module's power supply requires a power source that meets the following conditions:

Voltage:

100-240V

Frequency:

$50-60 \; Hz$

Current:

0.7A

**CAUTION**

Damage may result if a supply voltage is not within its specified range.

Chapter 1 5

#### **Connecting the AC Power Cord**

This is a Safety Class 1 Product provided with a protective earth ground incorporated into the power cord. The AC power cord is the device that disconnects the mains circuits from the mains supply. In addition, an external circuit breaker, readily identifiable and easily reached by the operator, should be available for use as the disconnecting device. Use the following steps to connect the AC power cord:

# WARNING Personal injury may occur if there is any interruption of the protective conductor inside or outside of the product. Intentional interruption is prohibited. CAUTION Damage to the product may result without adequate earth grounding. Always use the supplied three-prong AC power cord.

- 1. Ensure that the power cord is not damaged.

- 2. Install the product so that one of the following items is readily identifiable and easily reached by the operator: AC power cord, alternative switch, or circuit breaker.

- 3. Insert the mains plug into a socket outlet provided with a protective earth grounding.

#### **AC Power Cord Localization**

The AC power cord included with the module is appropriate for the final shipping destination. You can, however, order additional AC power cords for use in different areas: see "Replaceable Parts" on page 100.

#### **Proper Usage and Cleaning**

The N5102A module cover protects against physical contact with internal assemblies that contain hazardous voltages, but does not protect against the entrance of water. To avoid damage and personal injury, ensure that liquid substances are positioned away from your N5102A module.

| WARNING | Personal injury may result if the N5102A module is not used as specified. |

|---------|---------------------------------------------------------------------------|

|         | Unspecified use impairs the protection provided by the equipment. The     |

|         | N5102A module must be used with all means for protection intact.          |

#### **Cleaning Suggestions**

To prevent dust build-up that could potentially obstruct ventilation, clean the N5102A module cover periodically. Use a dry cloth, or one slightly dampened with water, to clean the external case parts.

**WARNING**

Electrical shock may result if the N5102A module is not disconnected from the mains supply before cleaning. Do not attempt to clean internally.

Chapter 1 7

#### Connecting the N5102A Module to the ESG/PSG

The N5102A module is used with an Agilent E4438C ESG<sup>1</sup> or E8267C PSG<sup>2</sup> signal generator; the signal generator provides baseband data to the interface module. This section provides information on connecting the N5102A module to the signal generator. While the graphics show an ESG signal generator, the procedure is the same for the PSG.

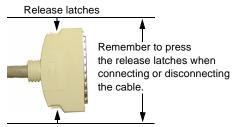

#### CAUTION

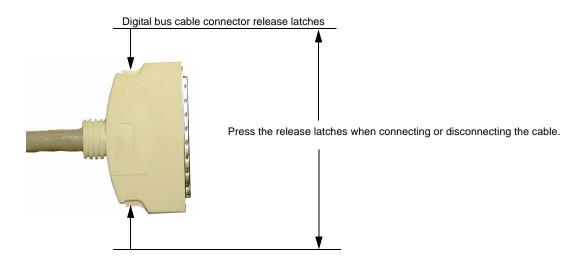

The digital bus cable connector has a release latch on each side (as shown below). To avoid connector damage, simultaneously squeeze both release latches when connecting or disconnecting the cable. A securely connected cable does not come loose when gently pulled.

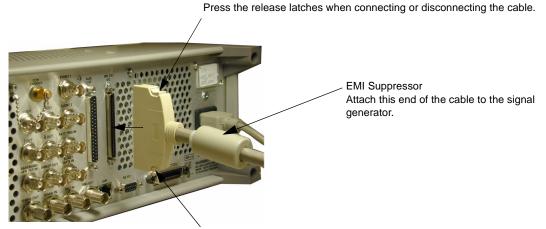

1. Refer to Figure 1-1. Connect the end of the digital bus cable that has the EMI suppressor to the signal generator's rear panel digital bus connector.

<sup>&</sup>lt;sup>1</sup>Requires Options 003 and either 601 or 602.

<sup>&</sup>lt;sup>2</sup>Requires Options 003 and 602.

#### NOTE

The digital bus connector may be labeled as DIGITAL BUS, DIG I/Q I/O, or DIGITAL I-Q I/O.

Figure 1-1 Signal Generator Digital Bus Cable Connection

Press the release latches when connecting or disconnecting the cable.

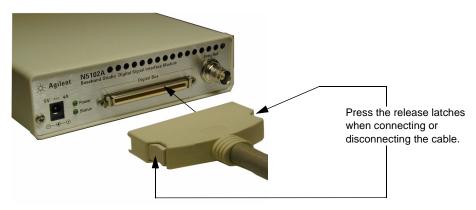

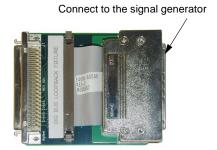

2. Refer to Figure 1-2. Connect the other end of the digital bus cable to the Digital Bus connector on the N5102A module.

The proprietary three meter cable enables you to place the interface module in a location close to the device under test (DUT).

Figure 1-2 N5102A Module Digital Bus Cable Connection

Chapter 1 9

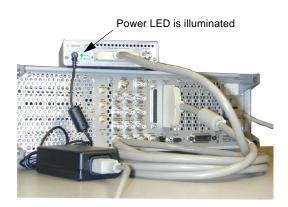

- 3. Refer to Figure 1-3. Connect the AC power cord to both the power supply and the AC power source (for details on connecting an AC power cord to an AC power source, see "Connecting the AC Power Cord" on page 6).

- 4. Connect the power supply to the N5102A module DC power receptacle.

Figure 1-3 N5102A Module Power Supply Connections

**AC Power Connection**

The power LED should be illuminated, indicating that the interface module is connected to the power source. If the power LED is not illuminated, check the AC power connection for the power supply and ensure that the DC power supply plug is fully inserted into the N5102A module DC power receptacle. If problems still persist after checking the power cords, refer to Chapter 6, "Troubleshooting," on page 93.

Figure 1-4 shows a completed installation.

Figure 1-4 Completed N5102A Module Installation

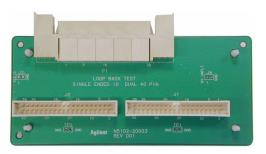

#### **Operation Verification**

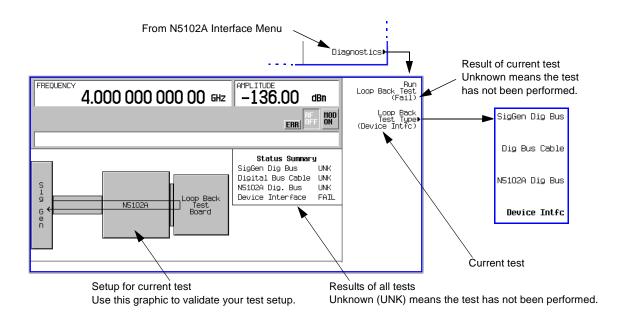

The N5102A module is configured and controlled using the user interface (UI) on the ESG/PSG signal generator. The operation verification uses the device interface test (Device Intfc), which is one of four interface module diagnostic tests, referred to as loop back tests. This loop back test checks the complete setup, providing a high level of confidence that the system is functioning properly. The three other tests are used if this test fails, and are described in "Running Diagnostic Tests" on page 96.

#### CAUTION

The Device Interface connector on the interface module communicates using high speed digital data. Use ESD precautions to eliminate potential damage when making connections.

- 1. Connect the N5102A module to the signal generator (as described in "Connecting the N5102A Module to the ESG/PSG" on page 8).

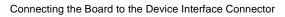

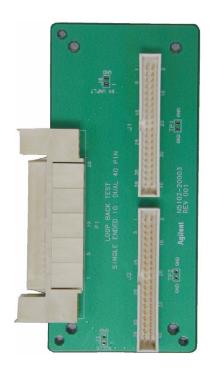

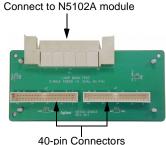

- 2. Refer to Figure 1-5. Connect the Loop Back Test Single Ended IO Dual 40 Pin board to the Device Interface connector on the rear panel of the N5102A module.

Figure 1-5 Connecting the Loop Back Board to the N5102A Module

Loop Back Test Single Ended IO Dual 40 Pin Board

The Loop Back Test Single Ended IO Dual 40 Pin board is used both for loop back testing, and as a break-out board to simplify the connection between the N5102A module and the DUT. When used for loopback testing, there should be no connections to the dual 40-pin connectors.

- 3. If the signal generator is not already on, turn it on.

- 4. On the signal generator, select the device interface test:

Chapter 1 11

Press Aux Fctn > N5102A Interface > Diagnostics > Loop Back Test Type > Device Intfc.

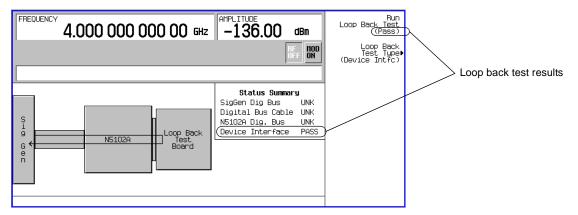

As shown in Figure 1-6, the currently selected test is displayed in parenthesis below the **Loop Back Test Type** softkey. Note also that the graphic provided displays the current test setup.

Figure 1-6 ESG/PSG Diagnostic Test Display

#### 5. Run the selected test: press Run Loop Back Test.

When the test completes, the results of the test (pass or fail) replaces unknown in both the parenthesis with the softkey and in the Status Summary display as shown in Figure 1-7. If this test fails, refer to "Running Diagnostic Tests" on page 96.

Figure 1-7 ESG/PSG Loop Back Test Result

#### **Regulatory Information**

#### **Statement of Compliance**

This product has been designed and tested in accordance with IEC Publication 61010, *Safety Requirements for Electronic Measuring Apparatus*, and has been supplied in a safe condition. The documentation contains information and warnings that must be followed by the user to ensure safe operation and to maintain the product in a safe condition.

#### **Assistance**

Product maintenance agreements and other customer assistance agreements are available for Agilent Technologies products. For any assistance, contact Agilent Technologies (see page 101).

#### Certification

Agilent Technologies certifies that this product met its published specifications at the time of shipment from the factory.

• this product does not require calibration

#### **Declaration of Conformity**

A declaration of conformity is on file for this product, and a copy is available upon request.

#### **Compliance with German Noise Requirements**

This is to declare that this instrument is in conformance with the German Regulation on Noise Declaration for Machines (Laermangabe nach der Maschinenlaermrerordnung –3.GSGV Deutschland).

Table 1-1 German Noise Requirements

| Acoustic Noise Emission/Geraeuschemission |                     |  |

|-------------------------------------------|---------------------|--|

| LpA < 70 dB                               | LpA < 70 dB         |  |

| Operator position                         | am Arbeitsplatz     |  |

| Normal position                           | normaler Betrieb    |  |

| per ISO 7779                              | nach DIN 45635 t.19 |  |

Chapter 1 13

# Installation Regulatory Information

#### **Compliance with Canadian EMC Requirements**

This ISM device complies with Canadian ICES-001. Cet appareil ISM est conforme a la norme NMB du Canada.

# 2 Overview

This chapter describes the features of the N5102A Baseband Studio digital signal interface module along with the signal generator options required to operate it.

- "Features" on page 16

- "Front Panel" on page 18

- "Rear Panel" on page 20

#### **Features**

The N5102A Baseband Studio digital signal interface module works with the Agilent E4438C ESG¹ or E8267C PSG² vector signal generators to provide a flexible digital interface for delivering digital baseband (IQ) or digital intermediate frequency (IF) test signals. The complex modulation formats of the signal generators, including W-CDMA, multitone, 1xEV-DV, WLAN and many more, are available at the bit level for testing digital components, transceivers, and subsystems. The N5102A module delivers the digital IQ or digital IF signals to your device with the data requirements, clock features, and signaling you need. With its selection of logic types and break-out board connectors, the interface module connects easily into your test system, in most cases eliminating the need for custom fixtures.

The N5102A module provides many features:

- bit level access to arbitrary waveform generator (ARB) and real-time signal generator baseband data from a wide range of signal creation applications

- simple user interface

- flexible data formats

- variable 4- to 16-bit word size

- serial, parallel, and parallel interleaved data transmission

- 2's complement or offset binary word representation

- MSB or LSB bit order

- digital IQ or digital IF signal

- flexible clocking

- automatic resampling

- 1 kHz to 100 MHz sample rate

- multiple clock inputs and outputs

- adjustable clock phase and skew

- multiple clocks per sample up to 4x

<sup>&</sup>lt;sup>1</sup>Requires Options 003 and either 601 or 602.

<sup>&</sup>lt;sup>2</sup>Requires Options 003 and 602.

- flexible signal interface

- multiple logic types provide single ended and differential testing capability—low voltage TTL (LVTTL), LVDS, and CMOS 1.5 V, 1.8 V, 2.5 V, and 3.3 V

- proprietary three meter cable connects the N5102A module to the signal generator

- interchangeable break-out boards

The parameters for the N5102A module are set using the UI on the ESG/PSG signal generators. This provides you with familiar UIs for both the modulation format and the interface module. Option 003 on the ESG/PSG enables the N5102A module UI.

With the N5102A module connected to the signal generator, you can perform multiple levels of testing. Since the baseband data that is provided to the interface module is the same data that can be modulated onto the RF carrier, this provides the benefit of performing early-stage testing of digital components and subsystems with the N5102A module, and then testing the integrated system using the modulated RF carrier.

Chapter 2 17

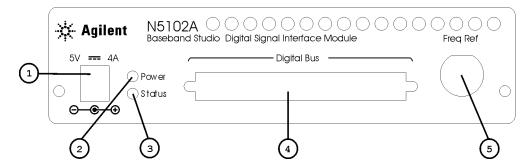

#### **Front Panel**

The baseband data and frequency reference inputs for the N5102A module are located on the front panel along with the receptacle for the DC power. A Power LED on the front panel indicates when DC power has been applied and a Status LED shows when the data lines are active.

Figure 2-1 Front Panel Features

#### 1. DC Power Receptacle

This receptacle accepts the DC power cord from the power supply. The DC power cord is shipped with the interface module.

#### 2. Power LED

This LED illuminates when DC power is supplied to the N5102A module.

#### 3. Status LED

The LED illuminates when the interface module is first turned on by pressing the N5102A Off On softkey located in the signal generator UI or after performing a module diagnostic test. Once lit, the LED stays on until the DC power is removed from the interface module. The LED conveys the status of the data lines and has two modes of operation:

Blinks Rapidly This indicates that the data lines are active and ready to transmit or are transmitting a digital signal.

Solid Illumination This shows that the data lines are inactive.

#### 4. Digital Bus Connector

This is the connector that the N5102A module uses to communicate with the ESG/PSG signal generator. A proprietary three-meter digital bus cable is supplied that connects to the Digital Bus connector and facilitates placing the interface module in a location close to the DUT.

#### 5. Freq Ref Connector

When Internal is the selected clock source, this 50 ohm connector accepts an external frequency reference at 3 dBm ±6 dB within the frequency range of 1 to 100 MHz that is used to generate the internal clock signal.

#### CAUTION

It is important that the signal generator, the interface module, and the DUT are locked to a common frequency reference. Failure to have a common frequency reference may result in a loss of data. See "Common Frequency Reference" on page 48 for information.

#### **Rear Panel**

The rear panel contains three connectors that are shown in Figure 2-2 and described in the following sections.

Figure 2-2 Rear Panel Features

#### 1. Ext Clock In Connector

This AC coupled 50 ohm connector is used for connecting an external clock source to the N5102A module. It accepts a signal with a nominal amplitude of 0 dBm and has a frequency range of 1 MHz to 400 MHz.

#### CAUTION

It is important that the signal generator, the interface module, and the DUT are locked to a common frequency reference. Failure to have a common frequency reference may result in a loss of data. See "Common Frequency Reference" on page 48 for information.

#### 2. Clock Out Connector

This 50 ohm connector outputs the clock signal at a nominal 400 mVp-p level with a frequency range of 100 kHz to 400 MHz. For a high impedance load of 5 k $\Omega$  or higher, the frequency range changes to 1 kHz to 100 kHz with a nominal output level of 2 Vp-p.

#### 3. Device Interface Connector

This connector interfaces with the DUT and supplies the digital IQ and digital IF signals in addition to sense lines, ground connections, a DC supply, and input and output clock signals. For more information on this connector including its pin-out, see "Device Interface Connector" on page 34.

#### **CAUTION**

The Device Interface connector on the interface module communicates using high speed digital data. Use ESD precautions to eliminate potential damage when making connections.

Chapter 2 21

#### Overview

**Rear Panel**

# 3 DUT Connections

This chapter provides information for the N5102A Baseband Studio digital signal interface module Device Interface connector, the supplied break-out boards, and the device interface mating connector to help simplify the DUT connection.

- "Break-Out Boards" on page 24

- "Device Interface Connector" on page 34

- "Device Interface Mating Connector" on page 39

#### **Break-Out Boards**

This section describes the different break-out boards and provides the pin-out for each one.

To maximize signal integrity, make the DUT connection as close as possible to the N5102A module Device Interface connector. The supplied break-out boards aid in minimizing this distance. Another solution is to incorporate the supplied device interface mating connector onto the DUT, eliminating the need for the break-out board and connecting cables.

Five interchangeable break-out boards are supplied to simplify the connection between the DUT and the N5102A module. The break-out boards connect to the Device Interface connector on the rear panel of the module and each comes with a different type of output connector. This provides a wide range of connection possibilities for the DUT. The break-out boards are easily identified by their output connector. If the situation arises where none of the break-out boards meet your needs, you can customize a connection solution using the supplied device interface mating connector. See "Device Interface Connector" on page 34 and "Device Interface Mating Connector" on page 39 for information. Table 3-1 lists the five break-out boards and the test type for which each is intended.

Table 3-1 Break-Out Board List

| Break-Out Board                               | Test Type    | Comment                                                                                                                                                             |

|-----------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single Ended I/O Dual 20<br>Pin               | Single-ended | 0.1 inch spaced header  This connector is commonly used for Agilent logic analyzer probe connections.                                                               |

| Differential I/O Dual 38 Pin                  | Differential | This connector is commonly used for Agilent logic analyzer probe connections.                                                                                       |

| Loop Back Test Single<br>Ended IO Dual 40 Pin | Single-ended | 0.1 inch spaced header  This board serves a dual purpose, in addition to serving as a break-out board for DUT connectivity, it is also used for diagnostic testing. |

| Single Ended I/O 68 Pin                       | Single-ended | Single SCSI style connector                                                                                                                                         |

| Differential I/O Dual 100<br>Pin              | Differential | This connector is commonly used for Agilent logic analyzer probe connections.                                                                                       |

The mating connectors for the outputs on the break-out boards are readily available from suppliers external to Agilent Technologies and are listed in Table 3-5 along with the connectors already mounted on the boards.

Table 3-2 Connector Part Numbers and Manufacturers

| Connector<br>Type        | Break-out Board Output<br>Connector Manufacturer<br>Part Number | Mating Connector<br>Manufacturer Part Number | Manufacturer     |

|--------------------------|-----------------------------------------------------------------|----------------------------------------------|------------------|

| 20-Pin                   | 2520-6002UB                                                     | 3421-6700 (wire connector)                   | 3M               |

| 38-Pin Mictor            | 2-767004-2                                                      | 767006-1 (board connector)                   | Tyco Electronics |

| 40-Pin                   | 2540-6002UB                                                     | 3417-6700 (wire connector)                   | 3M               |

| 68-Pin<br>D-Subminiature | 787170-7                                                        | 749621-7 (wire connector)                    | Tyco Electronics |

| 100-Pin Samtec           | ASP-65067-01                                                    | ASP-65267-02 (wire connector)                | Samtec           |

#### **Dual 20-Pin Break-Out Board**

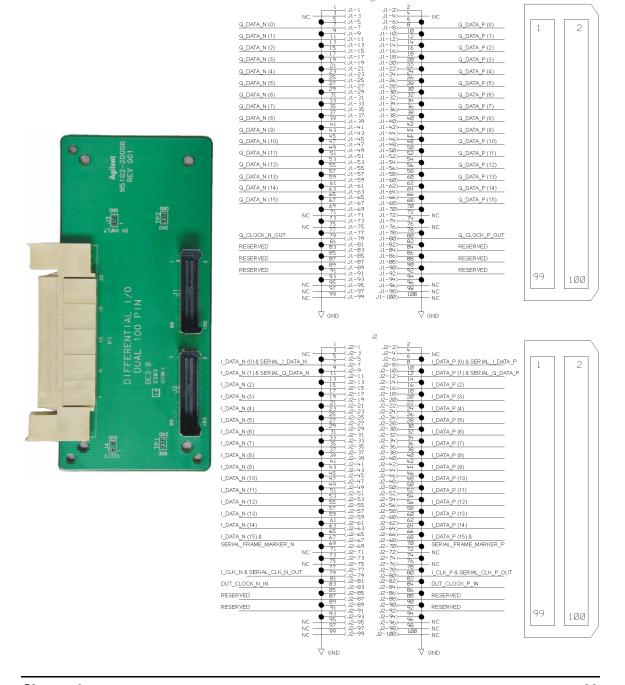

Use this break-out board when single-ended testing is required and there are minimal connection points. It is most suitable at lower sample rates using easily constructed ribbon cables. Figure 3-1 shows this board along with the pin-out for the output connectors. The 20-pin connectors are a common 0.1 inch spaced header. You can see in Figure 3-1 that the parallel I and Q signals are separated by connectors; J1 provides the Q signals and J2 provides the I signals. Notice that the serial signals are also provided on the J2 connector.

In order for the N5102A module to receive a clock through the Device Interface connector via this break-out board, a jumper wire is required at the 2 to C2 contacts. This is shown in Figure 3-1.

The VCCIO (selected high logic level voltage) is obtained at J3, while the + 5 volt unfiltered DC supply is acquired at J4.

Chapter 3 25

Figure 3-1 Dual 20-Pin 0.1 Spaced Connector

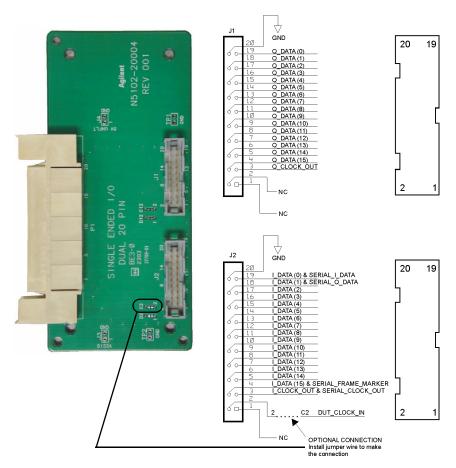

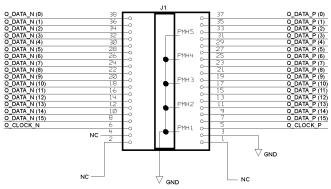

#### **Dual 38-Pin Break-Out Board**

Figure 3-2 shows this break-out board along with the pin-out for the output connectors. This board is intended for differential testing, however it can also be used for single-ended signals. For single-ended signals, the data is transmitted on the positive lines. Referring to Figure 3-2, notice that the parallel I and Q signals are separated by connectors; J1 provides the Q signals and J2 provides the I signals. The serial signals are also provided on the J2 connector.

In order for the N5102A module to receive a clock through the Device Interface connector via this break-out board, a jumper wire is required at the 2 to C1 contacts for a negative clock and at the 1 to C2 contacts for a positive clock. This is shown in Figure 3-2.

The VCCIO (selected high logic level voltage) is obtained at J4, while the + 5 volt unfiltered DC supply is acquired at J3.

Chapter 3 27

38

2

37

1

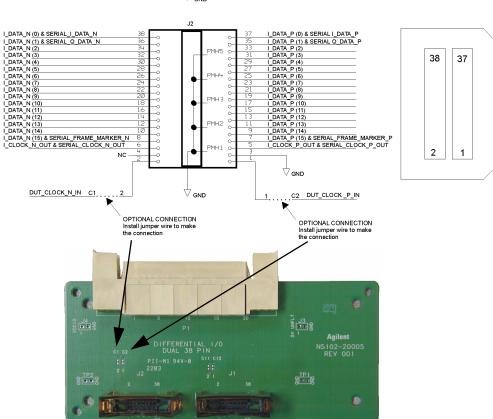

#### **Dual 40 Pin Break-Out Board**

This break-out board is useful for higher rate single-ended signals that benefit from a ground associated with each signal line. The 40-pin connectors are a common 0.1 inch spaced header. Figure 3-3 shows this break-out board along with the pin-out for the output connectors. Notice that the parallel I and Q signals are separated by connectors; J1 provides the Q signals and J2 provides the I signals. The serial signals are also provided on the J2 connector.

This board serves a dual function, one as a break-out board simplifying the connectivity of the DUT and the other as a loop back test board when performing a diagnostic test.

The VCCIO (selected high logic level voltage) is obtained at J3, while the + 5 volt unfiltered DC supply is acquired at J4.

Chapter 3 29

Figure 3-3 Dual 40 Pin 0.1 Spaced Header Connectors

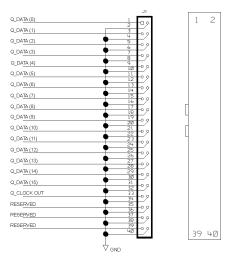

## Single 68-Pin SCSI Style Break-Out Board

Figure 3-4 shows this break-out board along with the pin-out for the output connector. This break-out board is intended for single-ended testing. The output connector is a SCSI style interface that is compatible with some existing products that provide a digital data output. The serial signals are transmitted on the I data lines.

In order for the N5102A module to receive a clock through the Device Interface connector via this break-out board, a jumper wire is required at the 66 to C2 contacts. This is shown in Figure 3-4.

The VCCIO (selected high logic level voltage) is obtained at J3, while the + 5 volt unfiltered DC supply is acquired at J4.

35 Q\_DATA (1) Q\_DATA (2) J1-2 J1-3 J1 - 36 J1  $\Diamond$ Q\_DATA (3) Q\_DATA (4) J1-4 J1-5 GND 40 Q\_DATA (5) Q\_DATA (6) J1-40 J1-6 J1-7 .11 - 4.1 >Q DATA (7) J1-42 J1-8 Q\_DATA (8) Q\_DATA (9) J1-43) J1-9 .11 - 44 > .11-10 Q\_DATA (10) J1-45 Q\_DATA (11) Q\_DATA (12) Q\_DATA (13) J1-46) J1-12 J1-47 J1-48 Q DATA (14) J1-493  $J1 = 15^{\circ}$ Q\_DATA (15)

I\_DATA (0) & SERIAL\_I\_DATA

I\_DATA (1) & SERIAL\_Q\_DATA JI-50> J1-161 JI-51 J1 - 52J1 - 18I\_DATA (2) J1-53> J1-19; I\_DATA (3) J1-54 J1-20; J1-55 J1-21) J1-22) I\_DATA (5) J1-56 > J1-57 > DATA (6) J1-58> I DATA (7 J1-241 I DATA (8) J1-59 J1-25 J1-26: J1-60> J1-61> I\_DATA (11) J1-62 L DATA (12) J1-63> 11-291 I\_DATA (13) J1-64) J1-30 J1-65> J1-31) I\_DATA (15) & SERIAL\_FRAME\_MARKER J1-66> .11 - 321 CLOCK\_P\_OUT J1-67 68 34 68 J1-68> .11 - 34 1 C2 DUT\_CLOCK\_IN 66 J1-PMH2 PMH2 GND√ OPTIONAL CONNECTION NC Install jumper wire to make the connection C2. 66 contacts PIN 67 TEST POINT GROUND GND♡

Figure 3-4 Single 68-Pin D-Subminiature SCSI Style Connector

Chapter 3 31

## **Dual 100-Pin Break-Out Board**

Figure 3-5 shows this break-out board along with the pin-out for the output connectors. It is intended for differential testing, however it can also be used for single-ended signals. For single-ended signals, the data is transmitted on the positive lines. You can see in Figure 3-5 that the parallel I and Q signals are separated by connectors; J1 provides the Q signals and J2 provides the I signals. Notice that the serial signals are also provided on the J2 connector.

The VCCIO (selected high logic level voltage) is obtained at J4, while the + 5 volt unfiltered DC supply is acquired at J3.

Figure 3-5 Dual 100-Pin Samtec Connector

Chapter 3 33

## **Device Interface Connector**

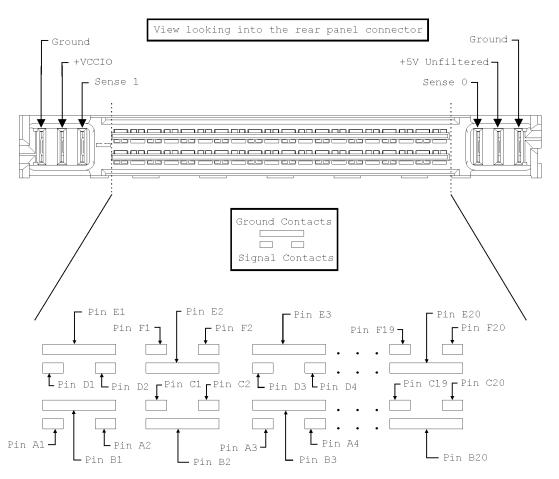

The figures and information shown in this section will facilitate customizing a connection solution for your DUT using the supplied device interface mating connector (see "Device Interface Mating Connector" on page 39). The signal contact layout for the Device Interface connector is shown in Figure 3-6 and the connector pin-out is shown in Figure 3-7 and Figure 3-8.

Figure 3-6 Device Interface Connector Layout

Figure 3-7 Device Interface Connector Pin-Out

| W1 X1 Y1 Z1 ←                                        | — GND                                                 |

|------------------------------------------------------|-------------------------------------------------------|

| W2 X2 Y2 Z2 ←                                        | +5V UNFILTERED                                        |

| W3 X3 Y3 Z3 ←                                        | — SENSE (0)                                           |

| C2Ø ← Q_DATA_P (1)<br>C19 ← Q_DATA_N (1)             | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| B2∅ ← G  A2∅ ← Q_DATA_P (3)  A19 ← Q_DATA_N (3)      | SND E20 ← Q_DATA_P (2)  119 ← Q_DATA_N (2)            |

| B19 ← G  C18 ← Q_DATA_P (5)  C17 ← Q_DATA_N (5)      | SND E19 ← GND  F18 ← Q_DATA_P (4)  F17 ← Q_DATA_N (4) |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | SND E18 ← Q_DATA_P (6)  D18 ← Q_DATA_N (6)            |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$  |

| B16 ← Q_DATA_P (11) A15 ← Q_DATA_N (11)              | □16 ← Q_DATA_P (10)<br>□15 ← Q_DATA_N (10)            |

| B15 ← — — — — — — — — — — — — — — — — — —            | $\begin{array}{cccccccccccccccccccccccccccccccccccc$  |

| B14 ← G_DATA_P (15) A13 ← G_DATA_N (15)              | □14 ← Q_DATA_P (14)<br>□13 ← Q_DATA_N (14)            |

| #13 ← G  C12 ← RESERVED  C11 ← RESERVED  #12 ← G     | $\begin{array}{cccccccccccccccccccccccccccccccccccc$  |

| A12 ← RESERVED A11 ← RESERVED                        | □12 ← RESERVED □11 ← RESERVED                         |

| B11 ← G                                              | SND E11 ← GND                                         |

Chapter 3 35

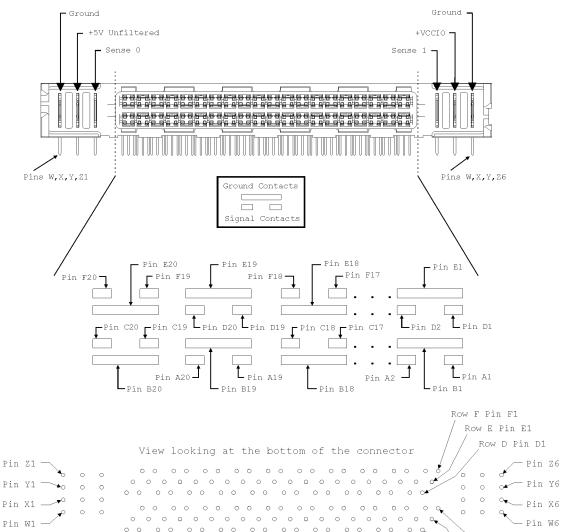

Figure 3-8 Device Interface Connector Pin-Out (continued)

| C1Ø ←          | I_DATA_P (1) & SERIAL_Q              | _DATA_P        | F1Ø ←  | I_DATA_P (0) & SERIA                     | L_I_DATA_P  |

|----------------|--------------------------------------|----------------|--------|------------------------------------------|-------------|

| C9 ←──         | I_DATA_N (1) & SERIAL_Q              | _DATA_N        |        | I_DATA_N (0) & SERIA                     |             |

| 81∅ ←          |                                      | GND            | E1∅ ←  |                                          | GND         |

| A 10 ←         | I_DATA_P (3)                         |                | DlØ←   | I_DATA_P (2)                             |             |

|                | I_DATA_N (3)                         |                |        | I_DATA_N (2)                             |             |

| В9 ←           |                                      | GND            | E9 ←   |                                          | - GND       |

| €8             | I_DATA_P (5)                         |                | F8 ←   | I_DATA_P (4)                             |             |

|                | I_DATA_N (5)                         |                | F7 ←   | I_DATA_P (4)                             |             |

| 88 ←           |                                      | GND            | E8 ←   |                                          | GND         |

| ₩8             | I_DATA_P (7)                         |                | D8 ←   | I_DATA_P (6)                             |             |

|                | I_DATA_N (7)                         |                |        | I_DATA_N (6)                             |             |

| B7 ←           |                                      | GND            | E7 ←   |                                          | GND         |

| C6 ←           | I DATA P (9)                         |                | F6 ←   | I DATA P (8)                             |             |

| C5 ←           | I_DATA_N (9)                         |                | F5 ←   | I_DATA_N (8)                             |             |

| B6 ←           |                                      | GND            | E6 ←   |                                          | - GND       |

| A6 ←           | I_DATA_P (11)                        |                | D6 ←   | I_DATA_P (10)                            |             |

| A5             | I_DATA_N (11)                        |                | D5 ←   | I_DATA_N (10)                            |             |

| B5 -           |                                      | GND            | E5 ←   |                                          | - GND       |

| C4 <del></del> | L DATA N (13)                        |                | F4     | L DATA P (12)                            |             |

| €3 ←           | —— I_DATA_N (13)<br>—— I_DATA_N (13) |                | F 3 ←  | —— I_DATA_P (12)<br>—— I_DATA_N (12)     |             |

| ₽4 ←           |                                      | GND            |        |                                          | - GND       |

| Λ4             | I_DATA_P (15) & SERIAL_I             | RAME MARKER E  | nu     | I DATA P (14)                            |             |

| Ã3             | I_DATA_N (15) & SERIAL_              | FRAME MARKER N | I D3 ← | —— I_DATA_P (14)<br>—— I_DATA_N (14)     |             |

| B 3 ←          |                                      | GND            | E 3 ←  |                                          | — GND       |

|                | DUT_CLOCK_IN_P                       | 0110           | E2/    | I CLOCK P & SERIAL                       | CLOCK P OUT |

| či←            | DUT_CLOCK_IN_N                       |                | F1     | I_CLOCK_P & SERIAL<br>I_CLOCK_N & SERIAL | CLOCK N OUT |

|                |                                      | GND            |        |                                          |             |

|                |                                      | 0110           |        | RESERVED                                 | 0.10        |

| A1             | RESERVED                             |                | D1 ←   | RESERVED                                 |             |

|                |                                      | CND            |        |                                          | — GND       |

| 2. (           |                                      | GIND           |        |                                          | OND         |

| W4 X4 Y4 2     | Z4 ←                                 | SENSE (1)      | )      |                                          |             |

|                |                                      |                |        |                                          |             |

| W5 X5 Y5 2     | Z5 ←                                 | +VCao          |        |                                          |             |

|                |                                      |                |        |                                          |             |

| W6 X6 Y6 2     | Z6 ←                                 | GND            |        |                                          |             |

# **Input and Output Clock Signals**

There are multiple output clock lines and two input clock lines to handle differential clocking. The N5102A module can be configured to accept the DUT clock through the Device Interface connector for data clocking. Using the input clock signal from the Device Interface connector is an alternative to using a clock signal applied to the Clock In connector. Table 3-3 lists the Device Interface connector pins for the different clock signals and the serial frame marker.

Table 3-3 Clock Signal and Serial Frame Marker Lines

| Clock Signal Type                  | Pin |

|------------------------------------|-----|

| Output Q-Clock Pos                 | F12 |

| Output Q-Clock Neg                 | F11 |

| Output I-Clock Pos                 | F2  |

| Output I-Clock Neg                 | F1  |

| Output Serial Clock Pos            | F2  |

| Output Serial Clock Neg            | F1  |

| Output Serial Frame Marker Pos     | A4  |

| Output Serial Frame Marker Neg     | A3  |

| Input Clock Signal (DUT Clock) Pos | C2  |

| Input Clock Signal (DUT Clock) Neg | C1  |

## **Data Lines**

There are 64 data lines on the Device Interface connector that allow for either differential or single-ended signals. These 64 data lines consist of 32-I lines (16 positive and 16 negative), and 32-Q lines (16 positive and 16 negative). Single-ended signals are routed on the positive data lines. Table 3-4 shows which data lines are used for a given signal.

Table 3-4 Data Lines

| Signal       | Serial Data                           |                                       | Parallel Data <sup>1</sup>                                                               |                                                                                                      |  |

|--------------|---------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|

| 3            | I                                     | Q                                     | I                                                                                        | Q                                                                                                    |  |

| Differential | Positive and negative lines: F9 & F10 | Positive and negative lines: C9 & C10 | Positive and negative lines 0–16 (A3–A10, C3–C10 D3–D10, F3–F10)                         | Positive and negative lines 0–16 (A13–A20, C13–C20, D13–D20, F13–F20)                                |  |

| Single-Ended | F10                                   | C10                                   | Positive lines 0–16 (A4, A6, A8, A10, C4, C6, C8, C10, D4, D6, D8, D10, F4, F6, F8, F10) | Positive lines 0–16 (A14, A16, A18, A20, C14, C16, C18, C20, D14, D16, D18, D20, F14, F16, F18, F20) |  |

<sup>1.</sup> Parallel interleaving (IQ and QI) occurs on the I data lines.

Chapter 3 37

# **DC Supply**

Referring to Figure 3-6, you can see that the interface module provides an unfiltered +5 volts DC supply through the Device Interface connector. This DC supply provides up to 100 mA and has a self-resettable fuse. You can use this DC current to bias components on the DUT where the noise will not compromise test results.

## **VCCIO**

The Device Interface connector also provides a connection for the VCCIO that can be measured at a test point on each break-out board. The VCCIO amplitude is equal to the high voltage level of the selected logic type.

# **Device Interface Mating Connector**

A mating connector for the Device Interface port is supplied to facilitate the DUT connection when none of the break-out boards provide a connection solution for your DUT.

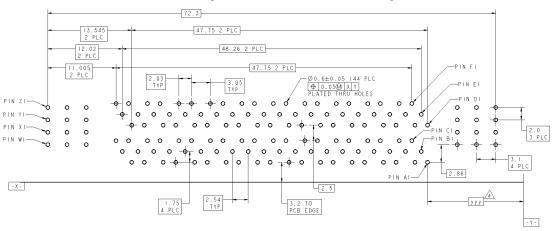

There are two ways to use the mating connector. One is to attach wires directly to the pins providing a quick connection solution. The other is to make a PC board with a footprint that matches the connector mounting pins. Figure 3-9 shows the layout of the signal contacts while looking directly into the connector and the pin footprint while viewing the connector from the bottom, and Figure 3-10 shows the connector footprint for a PC board.

The signal pin-out for the connector can be obtained from Figure 3-7 on page 35 and Figure 3-8 on page 36. These figures display the pin-out for the N5102A module Device Interface connector.

Table 3-5 provides the manufacturer and the part numbers for the Device Interface connector and its mate. Both connectors are readily available from suppliers external to Agilent Technologies.

**Table 3-5**

| Connector      | Connector Manufacturer | Mating Connector            | Manufacturer     |

|----------------|------------------------|-----------------------------|------------------|

| Type           | Part Number            | Manufacturer Part Number    |                  |

| 144-Pin Z-Dok+ | 1367550-5              | 1367555-2 (board connector) | Tyco Electronics |

Chapter 3 39

Figure 3-9 Z-Dok+ Device Interface Mating Connector Layout and Footprint

40 Chapter 3

Rows A, C, D, and F are signal contacts. Rows B and E are ground contacts.

Row C Pin C1

Row B Pin B1

Row A Pin A1

## Figure 3-10 Z-Dok+ Device Interface Mating Connector PC Board Foot Print

Component Side Shown

It is recommended that you check the Tyco Electronics web site for the most current PC board footprint drawing.

Rows A, C, D, and F are signal contacts. Rows B and E are ground contacts.

1 DIMENSIONS PER CUSTOMER BOARD LAYOUT.

Chapter 3 41

DUT Connections **Device Interface Mating Connector**

# 4 Operation

This chapter provides N5102A Baseband Studio digital signal interface module clock timing information and will guide you through configuring the digital signal parameters.

- "Clock Timing" on page 44

- "Connecting the Clock Source and DUT" on page 58

- "Operating the N5102A Module" on page 60

# **Clock Timing**

This section describes how clocking for the digital data is provided. Clock timing information and diagrams are supplied for the different port configurations (serial, parallel, or parallel interleaved data transmission) and phase and skew settings. All settings for the interface module are accomplished using the signal generator UI.

#### **Clock and Sample Rates**

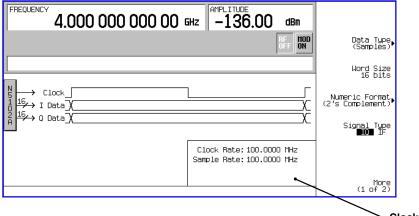

The clock is the signal that tells when the bits of a sample are valid. (A sample is a group of bits where the size of the sample is set using the Word Size softkey). The clock and sample rates are displayed in the first-level and data setup softkey menus for the N5102A module UI.

Figure 4-1 Data Setup Menu for a Parallel Port Configuration

Clock and sample rates

The N5102A module clock rate is set using the **Clock Rate** softkey and has a maximum range of 1 kHz to 400 MHz. The sample rate is automatically calculated and has a maximum range of 1 kHz to 100 MHz. These ranges can be smaller depending on:

- logic type

- · data parameters

- clock configuration

#### **Logic Type Output Levels**

The N5102A module maximum clock rate is dependent on the logic and signal type. However not all logic

type output levels are maintained to the maximum clock rate. Table 4-1 shows the warranted logic type output level clock rates and maximum clock rates for the logic and signal types. Notice that LVDS using an IF signal is the only logic type where the warranted and maximum rates are the same.

Table 4-1 Warranted Output Level Clock Rates and Maximum Clock Rates

| Logic Type     | Warranted Output | Level Clock Rates           | Maximum Clock Rates |                |  |

|----------------|------------------|-----------------------------|---------------------|----------------|--|

| Logic Type     | IQ Signal Type   | IF Signal Type <sup>1</sup> | IQ Signal Type      | IF Signal Type |  |

| LVTTL and CMOS | 100 MHz          | 100 MHz                     | 150 MHz             | 150 MHz        |  |

| LVDS           | 200 MHz          | 400 MHz                     | 300 MHz             | 400 MHz        |  |

<sup>1.</sup> The IF signal type is not available for a serial port configuration.

The output levels will degrade above the warranted output level clock rates, but they may still be usable.

#### **Serial Port Configuration Clock and Sample Rates**

For a serial port configuration, the lower clock rate limit is determined by the word size (word size and sample size are synonymous), while the maximum clock rate limit remains constant at 150 MHz for LVTTL and CMOS logic types, and 300 MHz for an LVDS logic type.

The reverse is true for the sample rate. The lower sample rate value of 1 kHz remains while the upper limit of the sample rate varies with the word size. For example, a five-bit sample for an LVTTL or CMOS logic type yields the following range values:

- Clock rate of 5 kHz to 150 Mhz

- Sample rate of 1 kHz to 30 MHz

Since a five-bit sample was used, a factor of five is used to calculate the minimum clock rate (5-bits x 1 kHz) and the maximum sample rate (150 MHz clock rate / 5-bits). Table 4-2 shows the serial clock and sample rate ranges for each word size.

Table 4-2 Serial Port Configuration Maximum Clock and Sample Rates

| Word Size | Logic Type: L\   | /TTL and CMOS     | Logic Type: LVDS |                   |  |

|-----------|------------------|-------------------|------------------|-------------------|--|

| (Bits)    | Clock Rate Range | Sample Rate Range | Clock Rate Range | Sample Rate Range |  |

| 4         | 4 kHz–150 MHz    | 1 kHz-37.5 MHz    | 4 kHz-300 MHz    | 1 kHz–75 MHz      |  |

| 5         | 5 kHz-150 MHz    | 1 kHz-30 MHz      | 5 kHz-300 MHz    | 1 kHz-60 MHz      |  |

| 6         | 6 kHz-150 MHz    | 1 kHz-25 MHz      | 6 kHz-300 MHz    | 1 kHz–50 MHz      |  |

| 7         | 7 kHz–150 MHz    | 1 kHz-21.4286 MHz | 7 kHz-300 MHz    | 1 kHz-42.8571 MHz |  |

| 8         | 8 kHz-150 MHz    | 1 kHz-18.75 MHz   | 8 kHz-300 MHz    | 1 kHz-37.5 MHz    |  |

| 9         | 9 kHz-150 MHz    | 1 kHz-16.6667 MHz | 9 kHz-300 MHz    | 1 kHz-33.3333 MHz |  |

| 10        | 10 kHz-150 MHz   | 1 kHz-15 MHz      | 10 kHz-300 MHz   | 1 kHz-30 MHz      |  |

| 11        | 11 kHz-150 MHz   | 1 kHz-13.6364 MHz | 11 kHz-300 MHz   | 1 kHz-27.2727 MHz |  |

| 12        | 12 kHz-150 MHz   | 1 kHz-12.5 MHz    | 12 kHz-300 MHz   | 1 kHz-25 MHz      |  |

| 13        | 13 kHz-150 MHz   | 1 kHz-11.5385 MHz | 13 kHz-150 MHz   | 1 kHz-23.0769 MHz |  |

| 14        | 14 kHz-150 MHz   | 1 kHz-10.7143 MHz | 14 kHz-300 MHz   | 1 kHz-21.4286 MHz |  |

| 15        | 15 kHz-150 MHz   | 1 kHz–10 MHz      | 15 kHz-300 MHz   | 1 kHz–20 MHz      |  |

| 16        | 16 kHz–150 MHz   | 1 kHz–9.375 MHz   | 16 kHz-300 MHz   | 1 kHz-18.75 MHz   |  |

## Parallel and Parallel Interleaved Port Configuration Clock and Sample Rates

Parallel and parallel interleaved port configurations have other limiting factors for the clock and sample rate ranges:

- logic type

- Clocks per sample selection

- IQ or IF digital signal type

Clocks per sample is the ratio of the clock to sample rate. For an IQ signal type, the sample rate is reduced by the clocks per sample value when the value is greater than one. For an IF signal, clocks per sample is always set to one. Table 4-3 shows the parallel and parallel interleaved port configuration clock and sample rates.

Table 4-3 Parallel and Parallel Interleaved Maximum Signal Ranges

| Clocks Per Signal Sample Type |      | Logic Type: L\   | /TTL and CMOS     | Logic Type: LVDS |                   |  |

|-------------------------------|------|------------------|-------------------|------------------|-------------------|--|

| Sample                        | Туре | Clock Rate Range | Sample Rate Range | Clock Rate Range | Sample Rate Range |  |

| 1                             |      | 1 kHz-100 MHz    | 1 kHz-100 MHz     | 1 kHz-100 MHz    | 1 kHz-100 MHz     |  |

| 2                             | IQ   | 2 kHz-150 MHz    | 1 kHz-75 MHz      | 2 kHz-200 MHz    | 1 kHz-100 MHz     |  |

| 4                             |      | 4 kHz–150 MHz    | 1 kHz-37.5 MHz    | 4 kHz-300 MHz    | 1 kHz-75 MHz      |  |

| 1                             | IF   | 4 kHz–150 MHz    | 4 kHz-150 MHz     | 4 kHz-400 MHz    | 4 kHz-400 MHz     |  |

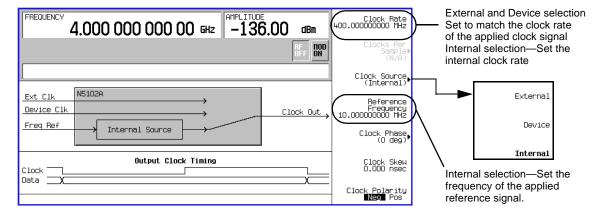

#### **Clock Source**

The clock signal for the N5102A module is provided in one of three ways:

- generated internally to the interface module

- provided externally via the Ext Clock In connector

- provided externally via the Device Interface connector

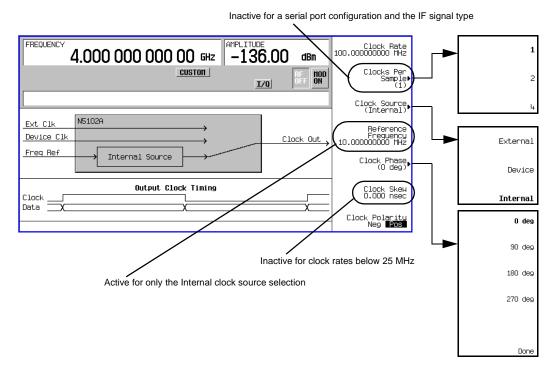

The clock source selection is accomplished using the N5102A module UI on the signal generator, see Figure 4-2.

Figure 4-2 Clock Source Selection

When you select a clock source, you must let the N5102A module know the frequency of the clock signal using the **Clock Rate** softkey. When internal is the clock selection, this softkey sets the internal clock rate; for

# Operation Clock Timing

the Device and External selections, this softkey must reflect the frequency of the applied clock signal.

When Internal is the clock source selection, a frequency reference is applied to the Freq Ref connector. The frequency of this applied signal needs to be entered using the **Reference Frequency** softkey, unless the current setting matches that of the applied signal.

Table 4-4 shows the clock source selections and the connector that accepts the externally applied signal along with the required softkey setting for each selection.

Table 4-4 Clock Source Settings and Connectors

| Clock Source          | Softkeys               |                         | N5102A Module Connection |              |                  |

|-----------------------|------------------------|-------------------------|--------------------------|--------------|------------------|

|                       | Reference<br>Frequency | Clock Rate <sup>1</sup> | Freq Ref                 | Ext Clock In | Device Interface |

| External              |                        | •                       |                          | •            |                  |

| Device                |                        | •                       |                          |              | •                |

| Internal <sup>2</sup> | •                      | •                       | •                        |              |                  |

For the Internal selection, this sets the internal clock rate. For the External and Device selections, this

tells the interface module the rate of the applied clock signal.

The selected clock source provides the interface module output clock signal at the Clock Out and the Device Interface connectors.

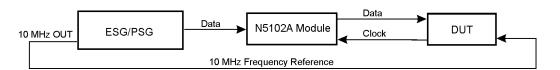

# **Common Frequency Reference**

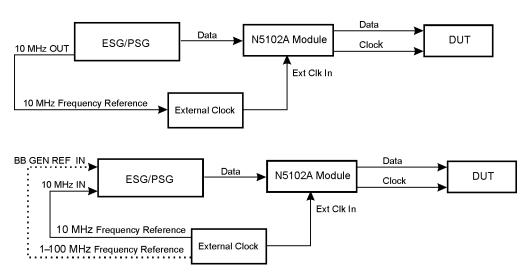

The clocking flexibility of the digital signal interface module allows the setting of arbitrary clock rates for the DUT. In general, the clock rate inside the ESG/PSG will be different from the interface module clock rate, so the interface module performs a rate conversion for clocking the data that is transmitted to the DUT. An important aspect of this conversion is to have accurate clock rate information to avoid loosing data. The module relies on relative clock accuracy, instead of absolute accuracy, that must be ensured by using a single frequency reference that is common to all clock rates involved in the test setup. This can be implemented in various ways (see the five drawings in Figure 4-3 on page 50), but whatever way it is implemented, the clock inside the signal generator must have the same base frequency reference as the clock used by the DUT.

When a frequency reference is connected to the signal generator, it is applied to one of two rear panel connectors:

- 10 MHz IN

- BASEBAND GEN REF IN

<sup>2.</sup> There should be no clock signal applied to the Ext Clock In connector.

The BASEBAND GEN REF IN connector will accept a frequency reference in the range of 1 to 100 MHz. In the situations where the external or DUT clock source can neither provide or accept a frequency reference, their clock signal can be applied to this same connector and used as the frequency reference.

Whenever an external clock signal or frequency reference is connected to the BASEBAND GEN REF IN connector, the frequency of the clock signal or the frequency reference needs to be entered into the signal generator modulation format being used. For information on the BASEBAND GEN REF IN connector for the ESG, refer to the *Agilent ESG Vector Signal Generator User's Guide*, and for the PSG, refer to the *Agilent PSG Signal Generators User's Guide*. For information on the associated softkeys and fields for entering the frequency of the applied clock signal or frequency reference, refer to the *Agilent ESG Vector Signal Generator Key and Data Field Reference* or the *Agilent PSG Signal Generators Key Reference* according to the signal generator being used.

Figure 4-3 Frequency Reference Setup Diagrams for the N5102A Module Clock Signal

## **Internally Generated Clock**

#### **Device (DUT) Supplied Clock**

**NOTE**: Use only one of the two signal generator frequency reference inputs.

## **Externally Supplied Clock**

**NOTE**: Use only one of the two signal generator frequency reference inputs.

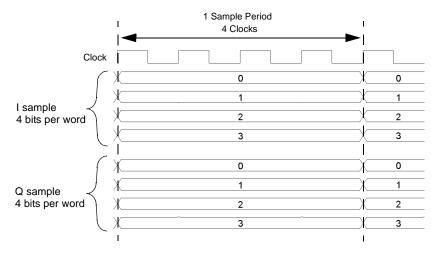

# **Clock Timing for Parallel Data**

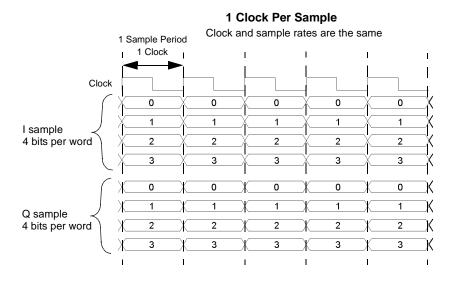

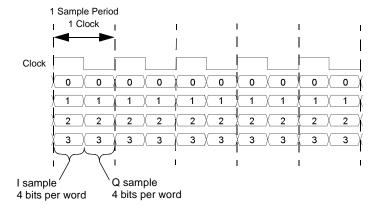

Some components require multiple clocks during a single sample period. (A sample period consists of an I and Q sample, and both are transmitted during a sample period). For parallel data transmissions, you have the option of selecting one, two, or four clocks per sample. For clocks per sample greater than one, the I and Q samples are held to accommodate the additional clock periods. This reduces the sample rate relative to the clock rate by a factor equal to the clocks per sample selection. For example, when four is selected, the sample rate is reduced by a factor of four (sample rate to clock rate ratio). Figure 4-4 demonstrates the clock timing for each clocks per sample selection.

Figure 4-4 Clock Sample Timing for Parallel Port Configuration

## 2 Clocks Per Sample

Sample rate decreases by a factor of two

#### 4 Clocks Per Sample

Sample rate decreases by a factor of four

## **Clock Timing for Parallel Interleaved Data**

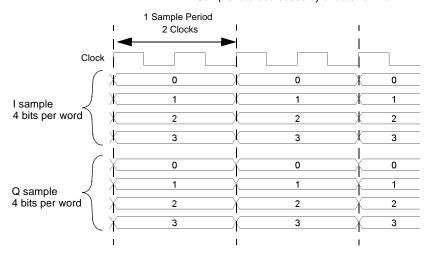

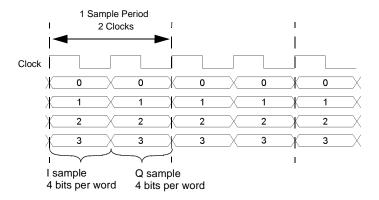

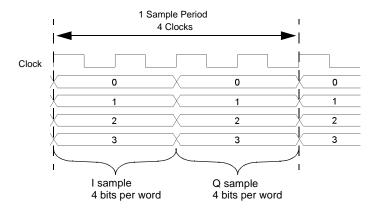

The N5102A module provides the capability to interleave the digital I and Q samples. There are two choices for interleaving, IQ where the I sample is transmitted first and QI where the Q sample is transmitted first. When parallel interleaved is selected, all samples are transmitted on the I data lines. This effectively transmits the same number of samples during a sample period on half the number of data lines as compared to non-interleaved samples. (A sample period consists of an I and Q sample, and both are transmitted during a sample period.) Clocks per sample is still a valid parameter for parallel interleaved transmissions and creates a reduction in the sample rate relative to the clock rate. The clocks per sample selection is the ratio of the reduction. Figure 4-5 shows each of the clocks per sample selections for a parallel IQ interleaved port configuration and the clock timing relative to the I and Q samples. For a parallel QI interleaved port configuration, just reverse the I and Q sample positions.

Figure 4-5 Clock Timing for a Parallel IQ Interleaved Port Configuration

#### 1 Clock Per Sample

The I sample is transmitted on one clock transition and the Q sample is transmitted on the other transition; the sample and clock rates are the same.

## 2 Clocks Per Sample

The I sample is transmitted for one clock period and the Q sample is transmitted during the second clock period; the sample rate decreases by a factor of two.

#### 4 Clocks Per Sample

The I sample is transmitted for the first two clock periods and the Q sample is transmitted during the second two clock periods; the sample rate is decreased by a factor of four.

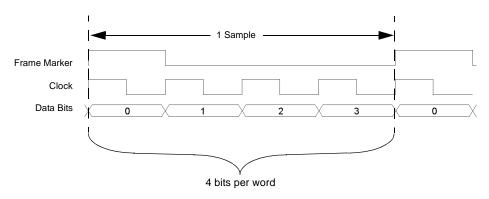

#### **Clock Timing for Serial Data**

Figure 4-6 shows the clock timing for a serial port configuration. Notice that the serial transmission includes frame pulses that mark the beginning of each sample where the clock delineates the beginning of each bit. For a serial transmission, the clock and the bit rates are the same, but the sample rate varies depending on the number of bits per word that are entered using the **Word Size** softkey. The number of bits per word is the same as the number of bits per sample.

Figure 4-6 Clock Timing for a Serial Port Configuration

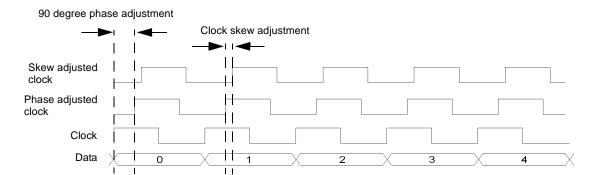

## **Clock Timing for Phase and Skew Adjustments**

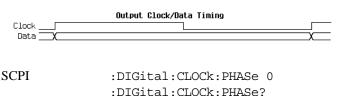

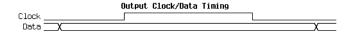

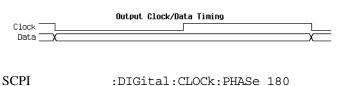

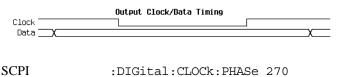

The N5102A module provides phase and skew adjustments for the clock relative to the data and can be used to align the clock with the valid portion of the data. The phase has a 90 degree resolution (0, 90, 180, and 270 degree selections) for clock rates from 10 to 200 MHz and a 180 degree resolution (0 and 180 degree selections) for clock rates below 10 MHz and greater than 200 MHz.

The skew is displayed in nanoseconds with a maximum range of  $\pm 5$  ns using a maximum of  $\pm 127$  discrete steps. Both the skew range and the number of discrete steps are variable with a dependency on the clock rate. The skew range contracts as the clock rate is increased and expands as the clock rate is decreased. The maximum skew range is reached at a clock rate of approximately 99 MHz and is maintained down to a clock rate of 25 MHz. For clock rates below 25 MHz, the skew adjustment is unavailable.

A discrete step is the resolution between each skew range value and is calculated using the formula:

$$\frac{1}{256 \times \text{Clock Rate}}$$

The number of discrete steps required to reach the maximum skew range decreases at lower frequencies. For example, at a clock rate of 50 MHz, 127 steps would exceed the maximum skew range of  $\pm 5$  ns, so the actual number of discrete steps would be less than 127.

Figure 4-7 is an example of a phase and skew adjustment and shows the original clock and its phase position relative to the data after each adjustment. Notice that the skew adjustment adds to the phase setting.

Figure 4-7 Clock Phase and Skew Adjustments

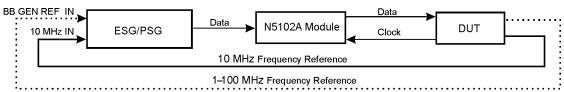

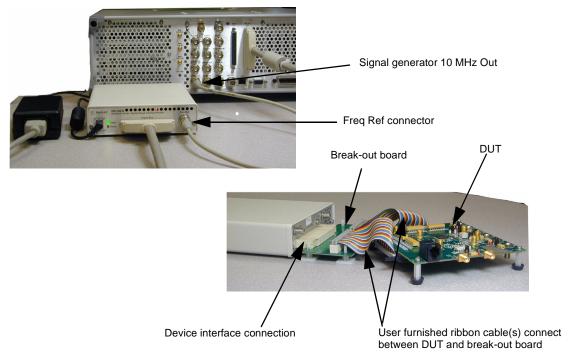

# **Connecting the Clock Source and DUT**

As shown in Figure 4-3 on page 50, there are numerous ways to provide a common frequency reference to the system components (ESG/PSG, N5102A module, and the DUT). Figure 4-8 shows an example setup where the signal generator supplies the common frequency reference and the N5102A module is providing the clock to the DUT.

#### **CAUTION**

The Device Interface connector on the interface module communicates using high speed digital data. Use ESD precautions to eliminate potential damage when making connections.

Figure 4-8 Example Setup using the ESG/PSG 10 MHz Frequency Reference

- 1. Refer to the five setup diagrams in Figure 4-3 on page 50 and connect the frequency reference cable according to the clock source.

- 2. If an external clock source is used, connect the external clock signal to the Ext Clock In connector on the interface module.

- 3. If the DUT incorporates the Device Interface mating connector, refer to Figure 4-8 for the device

interface connection and connect the DUT to the Device Interface connector on the N5102A module. Then proceed to "Operating the N5102A Module" on page 60.

- 4. If the DUT does not incorporate the Device Interface mating connector, select the break-out board that contains the output connector suited for your application.

- **5.** Refer to Figure 4-8 and connect the break-out board to the Device Interface connector on the N5102A module.

- 6. Connect the DUT to the break-out board.

# **Operating the N5102A Module**

This section shows you how to set the parameters for the N5102A module using the signal generator UI. Each procedure contains a figure that shows the softkey menu structure for the interface module function being performed. A quick reference setup checklist is also provided; see "Setup Checklist" on page 69.

## **Setting up the Signal Generator Baseband Data**

The digital signal interface module receives data from a baseband source and outputs a digital IQ or digital IF signal relative to the selected logic type. Because an ESG/PSG provides the baseband data, the first procedure in operating the interface module is configuring the ESG/PSG using either one of the real-time or ARB modulation formats, or playing back your own file using the Dual ARB player. For information on configuring the ESG, refer to the *Agilent ESG Vector Signal Generator User's Guide*, and for configuring the PSG, refer to the *Agilent PSG Signal Generators User's Guide*.

- 1. Preset the signal generator.

- 2. Access the modulation format (TDMA, Custom, etc.) and set the desired parameters.

- 3. Turn-on the modulation format.

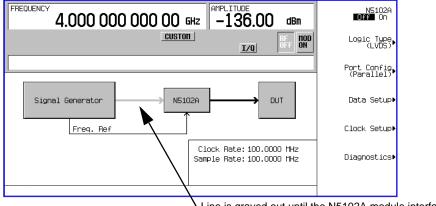

## Accessing the N5102A Module User Interface

All parameters for the N5102A module are set with the UI on the ESG/PSG signal generator.

Press Aux Fctn > N5102A Interface.

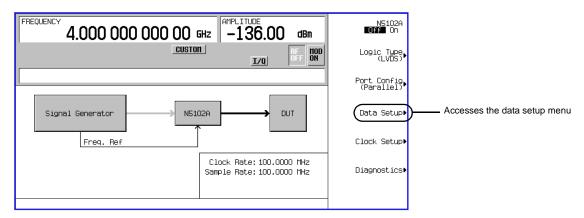

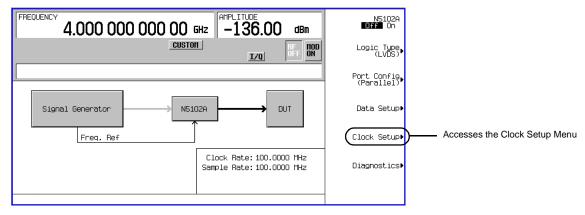

This accesses the UI (first-level softkey menu shown in Figure 4-9) for configuring the digital signal interface module. Notice that there is a graphic, in the ESG/PSG display, showing a setup where the N5102A module is generating its own internal clock signal. This graphic changes to reflect the current clock source selection.

Figure 4-9 First-Level Softkey Menu

Line is grayed out until the N5102A module interface is turned on

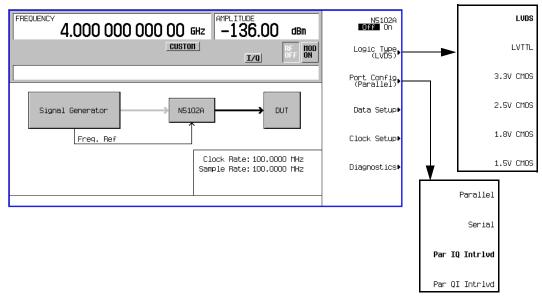

# **Choosing the Logic Type and Port Configuration**

Figure 4-10 Logic and Port Configuration Softkey Menus

Refer to Figure 4-10. Press the Logic Type softkey.

In this menu you can choose from a wide selection of logic types.

#### **CAUTION**

Changing the logic type can increase or decrease the signal voltage level going to the DUT. To avoid damaging the DUT and/or the N5102A module, ensure that both are capable of handling the voltage change.

The output levels for the logics types are not maintained to the maximum clock rates. See "Logic Type Output Levels" on page 44 for more information.

2. Select the logic type required for your DUT.

A caution message is displayed whenever you change logic types, and a softkey selection appears prompting you to confirm or cancel the logic type change.

- 3. Refer to Figure 4-10. Press the **Port Configuration** softkey.

- In this menu you can select either a serial, parallel, or parallel interleaved data transmission.

- Within the data and clock setup softkey menus, some softkeys function relative to the selected port configuration. So when you see softkeys that are grayed out, it generally means that they are not active for the current port configuration selection.

- 4. Select the port configuration for your DUT.

## **Selecting the Data Parameters**

This procedure guides you through the data setup menu. Softkeys that have self-explanatory names are generally not mentioned. For example, the **Word Size** softkey. For more information on all of the softkeys, refer to "Softkey and SCPI Command Descriptions" on page 72.

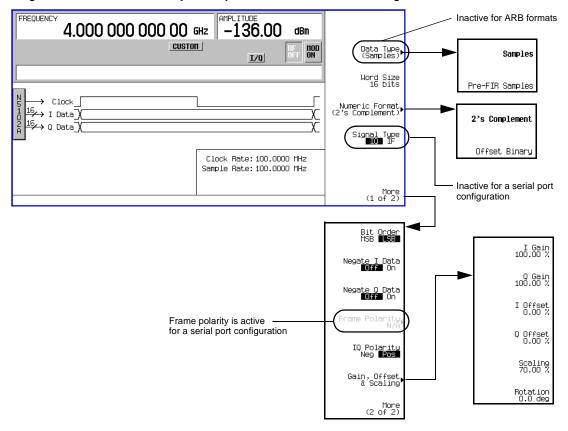

1. Refer to Figure 4-11. Press the **Data Setup** softkey.

Figure 4-11 Data Setup Menu Location

Within this softkey menu you can set the various parameters that govern the data received by the DUT. The status area of the display shows the number of data lines used for both I and Q along with the clock position relative to the data. When parallel or parallel interleaved is the port configuration, the number of data lines indicated is equivalent to the word (sample) size. When serial is the port configuration, the display will show that only one I and one Q data line is being used along with the frame marker that delineates the beginning of a sample. Figure 4-12 shows the data setup menu structure.

Figure 4-12 Data Setup Softkey Menu with Parallel Port Configuration

2. If you are using a real-time modulation format, press the **Data Type** softkey. (This softkey is inactive when an ARB modulation format is turned on.)

In this menu, you can select whether the real-time baseband data from the signal generator is either filtered (**Samples**) or unfiltered (**Pre-FIR Samples**). Your selection is dependent on your test needs and the DUT. The **Samples** selection provides FIR filtered baseband samples according to the communication standard (TDMA, W-CDMA, etc.) being used. This is the preset selection and the one most commonly

#### Operation

#### **Operating the N5102A Module**

utilized. However if the DUT being tested already incorporates FIR filters, the **Pre-FIR Samples** selection should be used to avoid double filtering.

- 3. Select the data type that is appropriate for your test needs.

- 4. Press the Numeric Format softkey.

From this menu, you can select how the binary values are represented. 2's complement allows both positive and negative data values. When components cannot process negative values, you can use the Offset Binary selection.